#### THE UNIVERSITY OF CALGARY

# PRACTICAL VERIFICATION AND SYNTHESIS OF LOW LATENCY ASYNCHRONOUS SYSTEMS

$\mathbf{BY}$

#### KENNETH S. STEVENS

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE

DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTER SCIENCE

CALGARY, ALBERTA SEPTEMBER, 1994

© KENNETH S. STEVENS 1994

# THE UNIVERSITY OF CALGARY FACULTY OF GRADUATE STUDIES

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies for acceptance, a thesis entitled: "Practical Verification and Synthesis of Low Latency Asynchronous Systems" submitted by Kenneth S. Stevens in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

| Dr. G. Birtwistle, Supervisor & Chairman<br>Department of Computer Science |

|----------------------------------------------------------------------------|

| Dr. J. W. Haslett Department of Electrical & Computer Engineering          |

| Dr. J. Kendall<br>Dean of Science, University of Calgary                   |

| Dr. P. Kwok<br>Department of Computer Science                              |

| Dr. L. E. Turner<br>Department of Electrical & Computer Engineering        |

| Dr. D. Edwards Department of Computer Science University of Manchester     |

#### Abstract

A new theory and methodology for the *practical* verification and synthesis of asynchronous systems is developed to aid in the rapid and correct implementation of complex control structures. Specifications are based on a simple process algebra called CCS that is concise and easy to understand and use. A software prototype CAD tool called *Analyze* was written as part of this dissertation to allow the principles of this work to be tested and applied. Attention to complexity, efficient algorithms, and compositional methods has resulted in a tool that can be several orders of magnitude faster than currently available tools for comparable applications.

A new theory for loose specifications based on partial orders is developed for both trace and bisimulation semantics. Formal verification uses these partial orders as the foundation of conformance between a specification and its refinement. The definitions support freedom of design choices by identifying the necessary behaviors, the illegal behaviors, and behaviors that are irrelevant. Loose specifications and their refinements are written using CCS semantics.

Pure CCS has been modified so that all of the common asynchronous hazard models – delay-insensitive, quasi delay-insensitive, speed-independent, and burst-mode – can be supported by Analyze. The parallel composition semantics have been extended to allow conjunctive broadcast communication. These communication primitives are implemented in a mixed-mode fashion so that pure CCS evaluation or hardware component modeling can be accomplished. A meta transition rule called *computation interference* is also implemented to strengthen the correctness of verifications under labeled transition systems such as CCS.

Congruences hold for conformance verifications in Analyze so that hierarchical verification is supported. A hierarchical top-down directed synthesis procedure is developed. Process logics are refined for practical applications of labeled transition systems to circuits and systems, including a new definition for liveness and deadlock. The target implementation methodology of this work is a parallel set of communicating burst-mode controllers. Burst-mode, developed earlier by the author, is formalized so that Analyze can verify when a specification obeys all the burst-mode rules and can be automatically synthesized into an implementation.

#### Acknowledgments

As an undergraduate I was fortunate to learn about asynchronous circuits from Al Davis at the University of Utah. This has developed into a disease that I cannot shake, and over 13 years later I am still designing asynchronous circuits and systems. I am also indebted to Al Hayes and Kent Smith, the two advisors for my master's thesis, who immersed me in VLSI, asynchronous circuits, and embedded systems.

After my master's thesis I was fortunate to get a second chance to learn from Al Davis by working for him on the Mayfly project at Fairchild and Hewlett-Packard. He has unquestionably been my greatest mentor, both professionally and recreationally. The satisfaction I achieved in my research with him was easily paralleled by the thrill of climbing a vertical frozen waterfall as he taught me ice climbing in the Canmore "Junkyards". Bill Coates, Robin Hodgson, Ian Robinson, Shane Robison, and Bic Schediwy deserve my thanks for their help, support, and friendship during the Post Office project.

Graham Birtwistle gladly took me on as a PhD student at the University of Calgary in spite of my rather low opinion at the time of the applicability of formal methods to circuit design. My "devil's advocate" side had been considerably bruised by the long hours of hand VLSI design on the Post Office, so when I arrived at Calgary I was very open to new approaches. Graham nursed me through my first real exposure to greek letters other than those attached to the front of fraternity houses. Jo Ebergen, Rob van Glabbeek, Faron Moller, and Chris Tofts contributed invaluable "formal" insights. I would like to thank John Aldwinckle and Ying Liu, classmates at the University of Calgary, for many hours of insightful technical presentations and

discussions, and for pulling me out of some tight jams. I would also like to thank my examiners, found on the Approval page, for their contributions and time.

Never have I worked with such a scholar and gentleman as Graham. Beyond the philosophical, technical, and organizational lessons he introduced me to a number of technical people whom I highly respect that have also become my friends. This is a typical exchange I copied from the whiteboard in Graham's lab, many of the entries coming from visitors he had brought in:

"Computer simulation is fun!"

"Simulation is the intelectual tool of last resort."

"At least us last resorters can spell intellectual."

"As long as they have little drinks with umbrellas in them, you can send me to the last resort!"

The atmosphere at Calgary was very good for my health and leisure as well as my intellect. Although Graham is twice my senior in years, I can barely keep up with him when he is on a mountain trail. I have even survived two of his races to the top of Mount Bourgeau and back during his Fall workshops. I would also like to thank Tom Fukushima as a great friend who took me to many of his favorite fishing holes, and Dave Spooner for keeping me in shape by dragging me off to the gym.

I would like to thank Hewlett-Packard for supporting this research through the generous scholarship funding of a Resident Fellowship. In particular I would like to thank Dick Lampman at HP Labs in Palo Alto, who is by far the best manager I have ever met. I miss his friendly visits as he applied "management by walking around" to perfection.

I would also like to thank my parents who let me and my family live in their cabin at beautiful Giles Flats in the Wasatch Mountains of Utah during the last few months of finishing my dissertation. The mountains were inspiring, but I think that perhaps my draw towards the fish in the creek squelched some of my literary inspiration.

Finally, God has blessed me with wonderful family – Dawn, Marina, Lincoln, and Lance. They have backed me in all my endeavors. None of this is worthwhile without them, and they will never know how much I love them.

Kenneth S. Stevens

k.stevens@ieee.org

September 1994

Giles Flats, Wasatch Mountains

### Contents

| A  | ppro                           | val Page                                 | ii   |  |  |

|----|--------------------------------|------------------------------------------|------|--|--|

| A  | Abstract iii Acknowledgments v |                                          |      |  |  |

| A  |                                |                                          |      |  |  |

| Li | ist of                         | Tables                                   | xii  |  |  |

| Li | ist of                         | Figures                                  | xiii |  |  |

| 1  | Int                            | roduction                                | 1    |  |  |

|    | 1.1                            | Asynchronous Design                      | 2    |  |  |

|    | 1.2                            | Circuit Design                           | 9    |  |  |

|    |                                | 1.2.1 Asynchronous Finite State Machines | 10   |  |  |

|    |                                | 1.2.2 Architectural Methodologies        | 11   |  |  |

|    |                                | 1.2.3 Macro Module Based Design          | 12   |  |  |

|    | 1.3                            | Silicon Compilation                      | 13   |  |  |

|    | 1.4                            | Formal Methods                           | 13   |  |  |

|    | 1.5                            | Automated Formal Asynchronous Design     | 14   |  |  |

|    | 1.6                            | The CCS Process Algebra                  | 16   |  |  |

|    |                                | 1.6.1 Syntax and Semantics of CCS        | 18   |  |  |

|    | 1.7                            | Thesis Structure                         | 21   |  |  |

|    | 1.8                            | Contributions                            | 23   |  |  |

| 2  | Mo                             | otivation for Analyze                    | 25   |  |  |

|    | 2.1                            | Overview of Mayfly and the Post Office   | 26   |  |  |

|    | 2.2                            | Asynchrony in Mayfly                     | 31   |  |  |

|    |                                | 2.2.1 Features                           | 31   |  |  |

|    |                                | 2.2.2 Problems                           | 32   |  |  |

|    | 2.3                            | Post Office Implementation               | 35   |  |  |

|    |                                | 2.3.1 Datapath Components                | 35   |  |  |

|    |                                | 2.3.2 Arbitration                        | 36   |  |  |

|    |                                | 2.3.3 Features                           | 37   |  |  |

|    |                                | 2.3.4 Difficulties and Design Flaws      | 38   |  |  |

|    | 2.4                            | Summary                                  | 42   |  |  |

| 3 | Ha  | zards                              |                                            | 46  |

|---|-----|------------------------------------|--------------------------------------------|-----|

|   | 3.1 | Delay                              | Models                                     | 47  |

|   | 3.2 | Hazar                              | d Models                                   | 49  |

|   | 3.3 | Circu                              | it Hazards                                 | 51  |

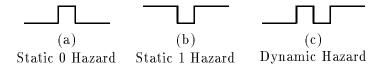

|   |     | 3.3.1                              | Hazard Occurrences                         | 53  |

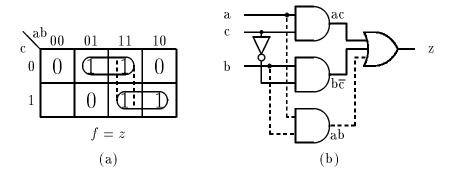

|   |     | 3.3.2                              | Hazards in Combinational Logic             | 53  |

|   |     | 3.3.3                              | Hazards in Sequential Automata             | 58  |

|   |     | 3.3.4                              | Delay Hazards                              | 61  |

|   |     | 3.3.5                              | Example of Hazards in Sequential C-element | 62  |

|   |     | 3.3.6                              | Other Potential Faults in the C-element    | 64  |

|   | 3.4 | Specia                             | fication Complexity and Hazards            | 66  |

|   | 3.5 | Hazar                              | d Summary                                  | 67  |

|   | 3.6 | Contr                              | olling Hazards                             | 72  |

|   | 3.7 | Hazar                              | ed Removal                                 | 73  |

|   |     | 3.7.1                              | Signal Reordering                          | 73  |

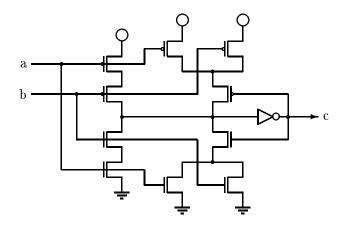

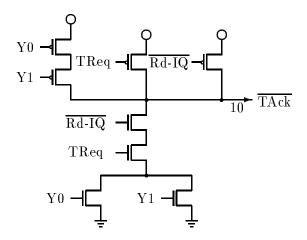

|   |     | 3.7.2                              | Complex Transistor Gates                   | 75  |

|   | 3.8 | Sumn                               | nary                                       | 78  |

| 4 | Bu  | rst-mo                             | de and AFSM Circuit Synthesis              | 80  |

|   | 4.1 | $\operatorname{Burst}$             | -mode                                      | 81  |

|   | 4.2 | CCS                                | Burst-mode Specifications                  | 83  |

|   | 4.3 | Funda                              | amental Mode Requirement                   | 86  |

|   | 4.4 | $\operatorname{Burst}$             | -mode Specifications                       | 88  |

|   | 4.5 | Burst                              | -mode Implementation Rules                 | 88  |

|   | 4.6 | Burst                              | -mode Specification Rules                  | 93  |

|   | 4.7 | Post (                             | Office Design Process Example              | 95  |

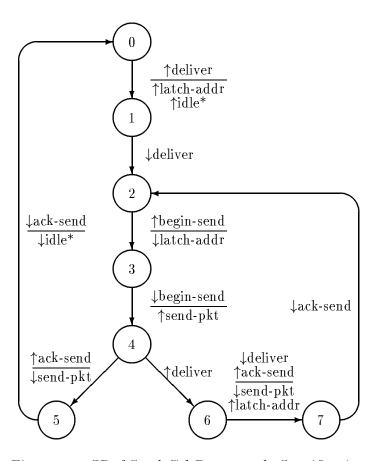

|   |     | 4.7.1                              | Asynchronous State Machine Design Example  | 96  |

|   | 4.8 | Sumn                               | nary                                       | 103 |

| 5 | Ha  |                                    | .1                                         | 105 |

|   | 5.1 |                                    | ntageous CCS Properties                    |     |

|   | 5.2 | Notat                              | ional Definitions                          | 109 |

|   | 5.3 | Equiv                              | alences and Agent Properties               | 113 |

|   |     | 5.3.1                              | CCS Equalities                             | 114 |

|   |     | 5.3.2                              | Predictability                             | 116 |

|   | 5.4 | $\operatorname{Hard}_{\mathbf{V}}$ | vare Conformance to Specifications         | 119 |

|   | 5.5 | Trace                              | Conformance                                | 121 |

|   |     | 5.5.1                              | Suitability of Trace Conformance           | 125 |

|   |     | 5.5.2                              | Strengthening Trace Verifications          | 127 |

|   |     | 5.5.3                              | Trace Failure Example                      | 129 |

|   |                          | 5.5.4           | Are Trace Systems Useful?                          |  |  |  | 132 |

|---|--------------------------|-----------------|----------------------------------------------------|--|--|--|-----|

|   | 5.6                      | Logic           | Conformance                                        |  |  |  | 136 |

|   |                          | 5.6.1           | Logic Conformance Example                          |  |  |  | 138 |

|   |                          | 5.6.2           | Properties of Logic Conformance                    |  |  |  | 139 |

|   | 5.7                      | Sumn            | nary                                               |  |  |  | 145 |

| 6 | $\mathbf{Pr}$            | actical         | Applications of Process Logics                     |  |  |  | 148 |

|   | 6.1                      | Henn            | essey-Milner Logic                                 |  |  |  | 149 |

|   | 6.2                      | Moda            | .l-μ Calculus                                      |  |  |  | 152 |

|   | 6.3                      | Appli           | cation Independent Invariant Properties            |  |  |  | 154 |

|   |                          | 6.3.1           | Deadlock                                           |  |  |  | 154 |

|   |                          | 6.3.2           | Liveness                                           |  |  |  | 157 |

|   | 6.4                      | Appli           | cation Specific Invariant Properties               |  |  |  | 160 |

|   |                          | 6.4.1           | Behavioral Proofs                                  |  |  |  | 160 |

|   |                          | 6.4.2           | Logical Conformance                                |  |  |  | 160 |

|   |                          | 6.4.3           | Operational Safety Proofs                          |  |  |  |     |

|   | 6.5                      | Confo           | ormance Applications                               |  |  |  | 167 |

|   | 6.6                      | Perfo           | rmance of Analyze                                  |  |  |  | 168 |

|   | 6.7                      | Sumn            | nary                                               |  |  |  | 171 |

| 7 | $\mathbf{S}\mathbf{y}$ : | $_{ m nthesis}$ | and Verification using Analyze                     |  |  |  | 173 |

|   | 7.1                      |                 | Concurrency Workbench                              |  |  |  | 175 |

|   | 7.2                      | Probl           | ems with CCS and the Workbench                     |  |  |  | 175 |

|   |                          | 7.2.1           | Parallel Conjunction                               |  |  |  | 180 |

|   |                          | 7.2.2           | Analyze Parsing                                    |  |  |  |     |

|   |                          | 7.2.3           | Circuit Connections                                |  |  |  | 186 |

|   |                          | 7.2.4           | Restriction and Relabeling                         |  |  |  | 187 |

|   | 7.3                      | Comp            | outation Interference                              |  |  |  |     |

|   |                          | 7.3.1           | Interference in a Specification                    |  |  |  | 190 |

|   |                          | 7.3.2           | Implementation Interference on an Output           |  |  |  | 190 |

|   |                          | 7.3.3           | Implementation Interference on a Restricted Signal |  |  |  | 191 |

|   | 7.4                      | Bisim           | ulation and Minimization                           |  |  |  |     |

|   |                          | 7.4.1           | Minimization and Equivalences                      |  |  |  | 192 |

|   |                          | 7.4.2           | Minimization Algorithm                             |  |  |  | 193 |

|   | 7.5                      | Analy           | vze Usage Example                                  |  |  |  | 196 |

|   | 7.6                      |                 | Level Synthesis                                    |  |  |  | 203 |

|   | 7.7                      |                 | -mode State Machine Verification                   |  |  |  | 207 |

|   | 7.8                      | Sumn            | narv                                               |  |  |  | 211 |

| 8  | Co    | lusions 215       |

|----|-------|-------------------|

|    | 8.1   | Challenges        |

|    |       | 1.1 Complexity    |

|    |       | 1.2 Tool Support  |

|    | 8.2   | Analyze Critique  |

|    | 8.3   | Tuture Directions |

|    |       |                   |

| Вi | bliog | phy 223           |

## List of Tables

| 2.1 | Mayfly Design Responsibilities                                  |

|-----|-----------------------------------------------------------------|

| 3.1 | A SIC Circuit Specification                                     |

| 3.2 | The TOGGLE Element                                              |

| 3.3 | One of Eight SI Delay Hazard Errors in the C-element 64         |

| 3.4 | Hazard Free Circuit Classes                                     |

| 4.1 | Different Burst Specification Styles                            |

| 5.1 | Traces of Length Three for the Two Element Hybrid Circuit 122   |

| 5.2 | Traces of Length Three for the Two Element FIFO                 |

| 5.3 | Failures for Some Matching Traces of the FIFO Example           |

| 6.1 | HML Formulae Testing a C-element                                |

| 6.2 | Distributed Arbiter Definition                                  |

| 6.3 | Erroneous Distributed Arbiter Interface                         |

| 6.4 | Specification for FIFO CSM Controller                           |

| 6.5 | Mutual Exclusion Element Specification                          |

| 6.6 | Modal- $\mu$ formulae for SI C-element Verification             |

| 6.7 | Modal- $\mu$ formulae for Burst-mode C-element Verification 168 |

| 6.8 | CCS Description of C-element Implementation                     |

| 6.9 | Performance of Analyze and Modal- $\mu$ Verifications           |

| 7.1 | CCS Description of Manchester Carry Chain                       |

| 7.2 | Parallel Conjunction Transition Rules                           |

| 7.3 | Hiding Transition Rules                                         |

|     |                                                                 |

# List of Figures

| 1.1<br>1.2<br>1.3                                           | Asynchronous Technology Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3                                           | Mayfly Processing Element Block Diagram.2'Mayfly Interconnection Topology29Photo Micrograph of the Post Office43                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

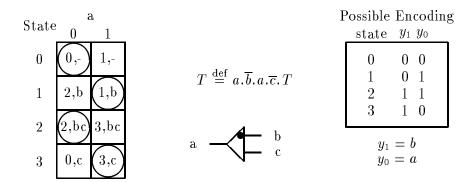

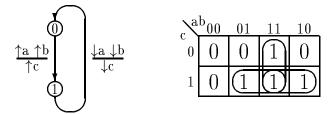

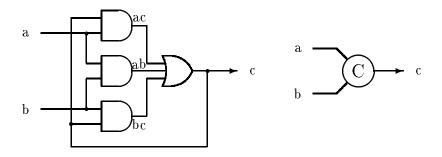

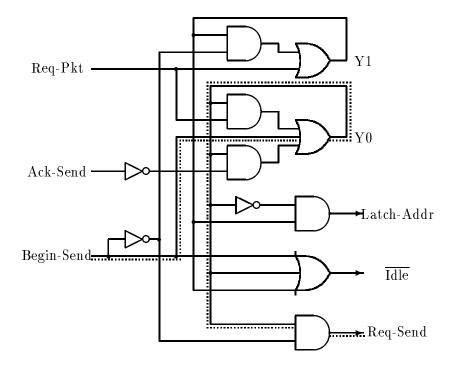

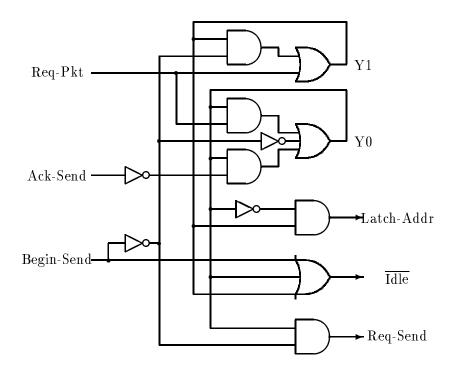

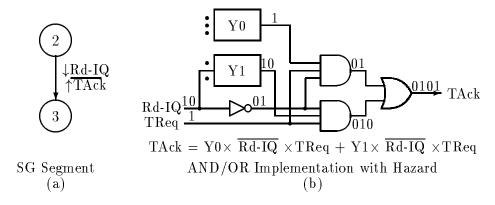

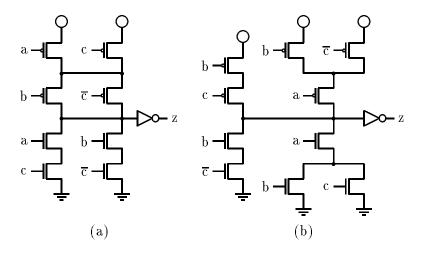

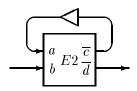

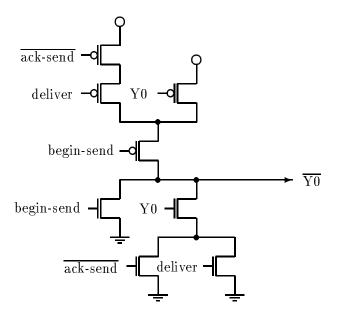

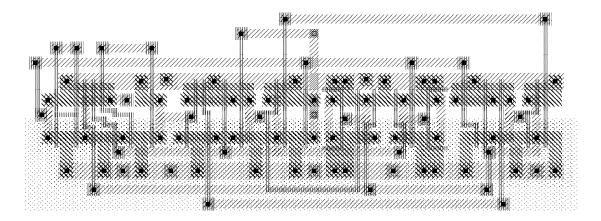

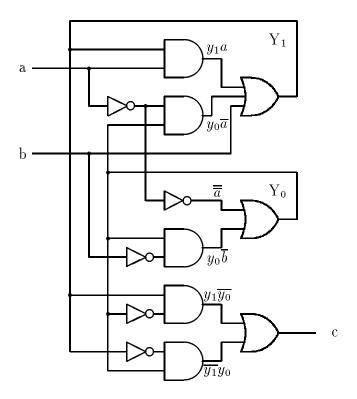

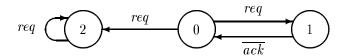

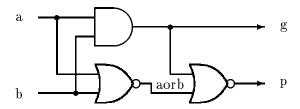

| 3.11                                                        | Hazards Waveforms in Combinational Logic 53 SIC Covering Example 55 Functional Hazard in a NAND Gate 56 Huffman and MEAT State Machines in the Post Office 56 C-element State Graph and K-map 65 C-element AND-OR Implementation and Logic Symbol 65 SBuf-Send-Ctl Circuit with a Transient Hazard 74 Burst-mode Hazard Free SBuf-Send-Ctl Logic 75 Complex Gate CMOS Transistor Implementation of C-element 76 PE-Send-Ifc Hazard . 76 PE-Send-Ifc Hazard Removal with Complex Gate 77 Hazard Free SIC Circuits as Complex Gate 76 Hazard Free SIC Circuits as Complex Gate 77 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                      | Burst-mode Conceptual Model83Burst-mode AFSM with Output Burst86Nacking Arbiter SIC State Machine Specification94SBuf-Send-Ctl Burst-mode Specification95Complex Gate Schematic for SBuf-Send-Ctl Y0105Layout of SBuf-Send-Ctl105                                                                                                                                                                                                                                                                                                                                               |

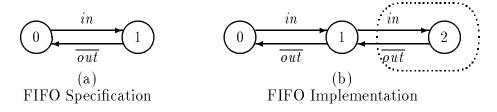

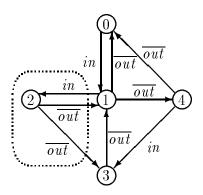

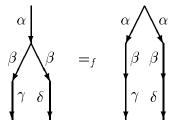

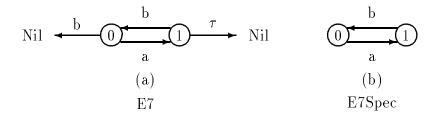

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Lattice of Equality Relations113Conformance Example with FIFO Buffers123Two FIFO Derivation Trees123Derivation Tree of FIFO-like Structure123Weaknesses in Trace Analysis126Weaknesses in Failures Semantics129E6 Circuit Description for Dill's Verifier130Falsely Verified Circuit E6133State Graph of Example E7133                                                                                                                                                                                                                                                          |

| 6.1                                                         | Weakly Deadlocking Handshake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.1 | Manchester Carry Chain                |

|-----|---------------------------------------|

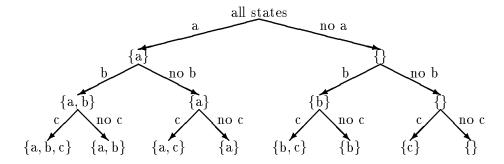

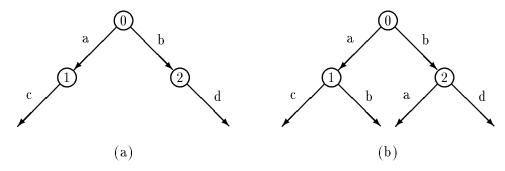

| 7.2 | Initial Bin Split for Minimization    |

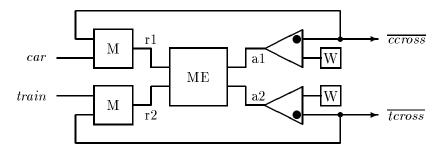

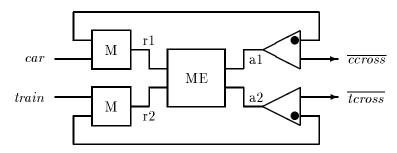

| 7.3 | Initial Crossing Decomposition        |

| 7.4 | Trace Crossing Decomposition          |

| 7.5 | Correct Crossing Decomposition        |

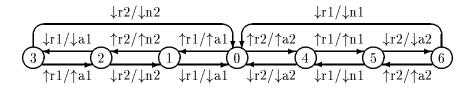

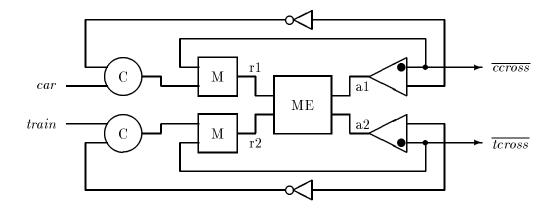

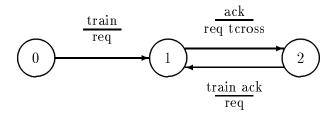

| 7.6 | Burst-mode Transition Graph for Train |

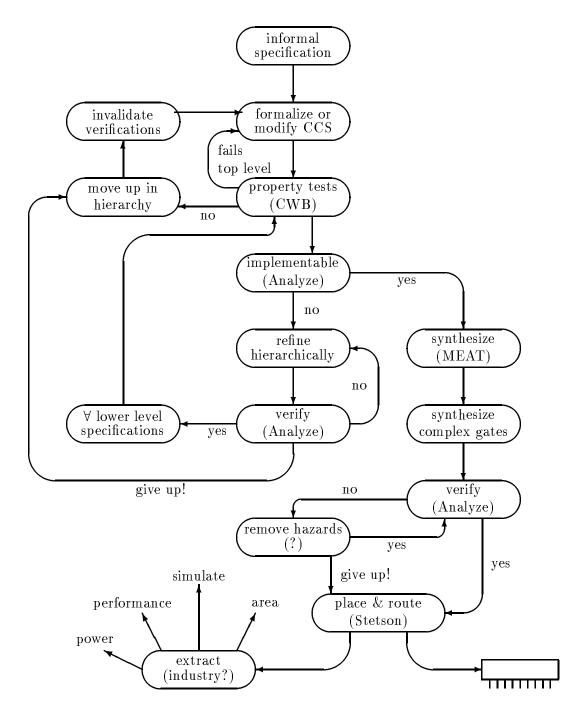

| 7.7 | Synthesis Procedure                   |

| 7.8 | Environmental Burst Constraints       |

#### Chapter 1

#### Introduction

Circuit design has undergone a tremendous explosion of progress in the last decade. In the early 1980's fabrication technology with a feature size of five microns permitted hundreds or thousands of devices to be fabricated on an integrated circuit. Today, millions of devices can be placed on a single circuit of the same area as the feature size has shrunk to half a micron or less.

The cost of designing integrated circuits has exploded as well. Modern fabrication facilities cost millions of dollars, and the man hours required to design a large circuit can be staggering.

Full custom design cannot keep up with the exponential increase in circuit complexity, as design cost and time to market will also increase dramatically, removing the market advantage of these designs for manufacturers. The need for improved tools and technologies that can rapidly produce correct circuits rivaling full custom performance and area advantages is clear from market and technology trends. The need for a designer's workbench capable of synthesis and verification was personalized for me after spending thousands of hours of manual implementation on a large, full custom, high performance, parallel integrated circuit.

The application of simplifying abstractions that can be upheld in implementations is the best method for supporting the explosive growth in design complexity. Increasing the level of abstraction lets a designer concentrate on architectural concepts rather than the micromanagement of devices and low level implementation details. The abstractions also facilitate the design automation and formal reasoning about circuit properties. The *digital* assumption is the most widely used abstraction for gates and transistors typically used in VLSI fabrication. Digital design assumes that the devices exist in one of two states, on or off, at high or low voltages.

Although transistors are not necessarily digital, this assumption can be accurate for well designed processes and circuits – high gain devices interconnected in a low-load fashion. These "digital" devices can be connected in such a way as to design more complex *combinational* functions that are themselves digital. A combinational function is one that solely depends on the input set to determine the output function. This reasoning can accurately be employed for circuit synthesis.

#### 1.1 Asynchronous Design

Many functions cannot be represented in a combinational fashion because they rely on the *history* of input sequences. Such logic is called *sequential* logic. How operations are *sequenced* provides the first and largest distinction between digital design styles. There are two fundamental methods of sequencing these circuits – synchronously or asynchronously.

Synchronous digital circuits assume that time is divided into global, distinct, discrete periods that are controlled by the metronomic tick of a global clock. Control and data signals are stored and passed in lockstep on fixed intervals as determined by the clock and its phases. Storage and sequentiality is typically introduced with clocked latches. All logic functions between the latches must be evaluated during the clock period or the circuit will fail.

Asynchronous circuits do not base their sequencing on regular time. Rather, an interface is defined such that function initiation and completion are explicitly signaled. These interfaces always embody handshaking to ensure that both the sender and receiver of the communication are ready. This interface protocol is commonly referred to as a request/acknowledge handshake. This formal handshake protocol simplifies the design and verification of asynchronous circuits by breaking them into hierarchical modules. The difficult task of creating large parallel systems is greatly simplified since no global analysis is required. Such systems are created by composing and interconnecting the formal interfaces of parallel modules, and verified by proving the interface protocols are upheld. The clean, formal interfaces of asynchronous logic come at the cost of increasing the difficulty of module design as the handshake signals must be free of all glitches and hazards. Hence the more difficult system design aspects are simplified by asynchronous circuits, and the easier challenge of module design becomes more complicated.

Asynchronous circuits are not slaves to a single unifying master (the clock) as are synchronous systems. Clocked, or synchronous, systems can be easily and reliably controlled inside an asynchronous formalism. Much of my early asynchronous design was based on stoppable clocks we termed "Chuck clocks" in honor of their inventor Chuck Seitz. The controlling asynchronous logic views the clocks as request or acknowledge handshakes, and the clocked domain can be fully synchronous. Such mixed mode designs are formally termed self-timed. Some timing analysis must be done to assure that the asynchronous control is always prepared to accept the clock handshake given the clock circuit's known frequency. Other delay models are introduced in Chapter 3.

The task of asynchronous controllers is to correctly accept and sequence handshaking signals. Datapath logic must also generate handshakes one of two ways: as true completion signals generated by side effect from the logic operations, or through delay elements that model the timing characteristics of the function. Completion signals are preferable as they accurately model the actual delays in the devices. At times true completion signals can be generated at very little additional complexity. For instance, ORing the two bit lines of precharged RAM cells will produce a handshake indicating the successful completion of the charging and the data valid operations. A good example of the use of delay approximations comes from Sutherland's 1988 Turing Award lecture on the micropipeline architectural style [Sut89]. A delay simulates the operational time for each pipeline stage and is used to control the following stage. Delay approximations permit the utilization of standard (synchronous) datapath components, but the designs will not be as robust. When true completion signals are not generated, the timing analysis can be done locally; the functional interfaces remain intact, supporting modular design and verification.

Data transmission is typically carried out using one of two methods: a **bundled** data protocol which requires assumptions on the transmission delays of the data and its associated handshake signals, or with data encoding techniques such as the dual rail protocol which encodes the completion signal with the data. Bundled data protocols contain parallel data and handshake paths, and the transmission delays of the two paths should be *equipotential*, or nearly identical. The data is then transmitted before the handshake signal, with the assumption that the handshake will be observed at the destination following the arrival of the data. This places a constraint on the drivers, layout, routing, and loading of the signals. Data encoding

protocols use more than one wire per data bit to encode data validity as well as a digital value. This method is more robust and simplifies the layout and routing at the cost of doubling the number of wires required to transmit data.

The asynchronous design style results in the following advantageous circuit properties:

- 1. Control is localized, supporting modular hierarchical designs. Some global circuit issues such as the power carrying capacity of metal lines and timing analysis are simplified, while others such as clock skew are moot.

- Power is actively expended only when a module is actively controlling or processing information. Well designed modules only consume leakage current when idle.

- 3. Performance can be improved as there is no need to wait for a clock edge to begin processing a transaction, and latency can be the device and ambient minimum. Performance estimates and run times for asynchronous circuits result in average delays for the data values rather than requiring worst case values for reliability.

- 4. Asynchronous inputs and interrupts are a natural aspect of asynchronous design, and will not result in synchronization failures.

- 5. The circuits are extremely robust because they can adapt to the ambient environment. Changes in temperature, voltage, and implementation parameters will not effect the correctness of the circuit's functions. For example, a hazard free asynchronous circuit designed in scalable rules can operate correctly in a

2 micron or 0.5 micron process, at a temperature of 30°C or immersed in liquid nitrogen, and at varying voltages. Modifying these parameters can effect the power consumption and performance dramatically.

- 6. The interfaces can be extremely robust, including the adaption to timed protocols [MCS94].

- 7. Fewer constraints may be required regarding the physical placement and routing of cells, simplifying implementation details.

- 8. Observability may be easier to achieve using the stuck-at fault model because a handshake signal that cannot make a transition results in deadlock. While faults are commonly observable by this method in practice, a more rigorous theory for fault coverage is required for the differing asynchronous design methodologies.

These advantages have positive ramifications for increasing the level of abstraction that is desperately needed for large high performance designs. Certain aspects of tool development – such as place and route software and timing analysis – can be simplified. However, several aspects of asynchronous design also present challenges.

1. Hazard free design is a difficult, complex process – particularly when using unbounded delay models. Synchronous synthesis and analytical tools are typically not applicable to asynchronous designs because algorithmic assumptions may require the side effects of a global clock, or they do not avoid or detect hazards. Asynchronous designs are also more difficult to create using ad hoc approaches.

- 2. Although it is difficult to make accurate comparisons, asynchronous designs are probably larger, and therefore more expensive to fabricate, than comparable synchronous designs. Clock lines and drivers are not present in asynchronous designs. However, most implementations require hazard removal techniques that add logic gates. The handshake signals also add wires between logic components. The circuit area of VLSI designs is more sensitive to the wiring requirements than the number of transistors, and it is difficult to project the tradeoff between the reduction in wire complexity due to clock removal versus the increase due to handshake lines. The additional area overhead supposedly varies from 5%–20% for custom designs, and up to 100% for designs synthesized using programming techniques. The overhead is much worse for data-intensive architectures when data encoding techniques (such as dual rail protocols) are used.

- 3. The handshake protocol is only effective over short distances, because the delay of transmitting a signal is usually proportional to the distance of the transmission. One would not use handshaking protocols for satellite transmissions! Although functionality is not compromised, there is a significant performance sensitivity to the placement of modules. There may also be a performance degradation for level sensitive return-to-zero (or four-cycle) protocols versus the transition based non-return-to-zero (or two-cycle) protocols when the additional handshake cycles cannot be hidden in the computation phase.

The greatest disadvantage comes not from any theoretical disability, but rather from the serious deficiency in tools tailored for asynchronous design practices and a lack of experience and case studies. This deficiency comes in all areas: simulation, synthesis, verification, and testing. The following sections discuss some of the significant progress recently achieved in asynchronous theory, architecture, and tools by a small core of researchers and engineers.

Research into asynchronous circuit design has been carried out sporadically since the early 1950's. Most of the modern theory is founded on the early work done by Huffman, Muller, and Unger [Huf57, Mil65, Ung69]. Although asynchronous systems such as the Illiac [Geo68] had proven asynchronous technology as a viable approach, interest waned in asynchronous design. Clocked systems were much easier to design since hazards did not need to be removed or controlled. The low integration and complexity of the devices allowed global analysis to be carried out efficiently.

Al Davis, Charles Molnar, Chuck Seitz, and Ivan Sutherland bucked the trend with their pioneering work in asynchronous systems [Dav77, CM72, MFR85, MC80, SMSM79]. Technological trends, including the ever increasing levels of integration of circuits, and the maturing of logic systems and formal methods have resulted in a new wave of interest and applicability in these novel circuits.

I studied asynchronous circuits under Al Davis in the early 1980's and have had the fortune of learning from Molnar, Seitz, and Sutherland. In the mid 1980's I joined a team designing a distributed memory multiprocessor called *Mayfly*. This gave me the opportunity to take my asynchronous circuit experience out of the academic world into industry with the development of a high speed CMOS VLSI communication coprocessor chip called the *Post Office*. The techniques at that time for hazard removal or control required a single input change constraint, large delays, or performance inhibiting flip flops [Ung69, CD73]. Since the performance of the Post Office

was critical to the success of the Mayfly project, an alternative method of producing low latency control was needed. This led me to develop a new asynchronous control methodology called **burst-mode** which was successfully applied in all controllers of the Post Office.

During the development of the Post Office, interest in asynchronous designs was widely renewed in the academic community on three different fronts. Circuit designers found it ever more difficult to cope with the global constraints of synchronous design and had begun to seriously investigate asynchronous approaches. Software engineers began taking advantage of the modularity of asynchronous circuits to build program based asynchronous synthesis tools. Logicians and mathematicians discovered that asynchronous circuit design is a natural and useful application for their theories. The coming together of these three fields has resulted in a new renaissance of asynchronous design theory.

The next sections present some of the salient achievements of these three groups.

#### 1.2 Circuit Design

One of the most challenging aspects of asynchronous circuit design is the removal of hazards from circuits. Since all hazards cannot be removed before layout with unbounded delay models, the ability to *control* the occurrence of the remaining hazards is also of paramount importance. The following general techniques have been applied to the direct layout of asynchronous circuits with attention to hazard removal and control.

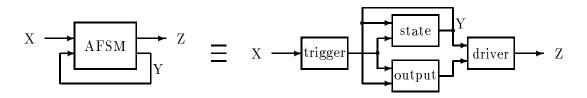

#### 1.2.1 Asynchronous Finite State Machines

The asynchronous finite state machine (AFSM) based methods take operational descriptions as inputs and produce circuit descriptions as outputs. These methods are typically targeted for CMOS design, creating gate or transistor level circuits. The primary goal of these systems is to produce circuits that are free from as many hazards as possible through compilation techniques, while also minimizing the latency and area of the implementation. This method is targeted for performance sensitive applications. While it is not possible to remove all sequential hazards using the unbounded delay model (see Chapter 3), these methods stand out as producing systems with the greatest performance with relatively few constraints required for hazard control.

They achieve the best performance and smallest size of all the design methods when moderately complex specifications are used. Unfortunately, most of the AFSM based tools use informal operational definitions such as state graphs, which limits the ability to reason about complex systems of AFSMs.

Most of these methods have adopted the burst-mode methodology to achieve higher performance with the smallest exposure to hazards. The most efficient circuits are typically created from descriptions containing from 5 to 32 burst-mode states. While these methods are typically used for control synthesis, they can also be applied to the creation of datapath logic.

The first burst-mode synthesis tool was developed by Bill Coates, Al Davis, and myself to aid in the design of the Post Office [CDS93a, CDS93b]. The tool was dubbed the "Most Excellent Asynchronous Tool" (MEAT) after being inspired by

the movie "Bill and Ted's Excellent Adventure". MEAT was used in the development of 90% of the control modules in the Post Office. A quick introduction to the AFSM synthesis capabilities of MEAT can be found in Section 4.7.

The MEAT prototype did not remove all combinational hazards. A flaw was pointed out by Steve Nowick, who in the process proved that the burst-mode methodology permits the synthesis of totally hazard-free *combinational* logic [ND92]. Nowick also went on to produce a burst-mode synthesis system using local clocks [ND91a] as part of his Stanford dissertation. This interaction with Stanford also resulted in another burst-mode synthesis system [YD92].

A widely known method for formalizing and synthesizing AFSMs was developed by Chu based on *signal transition graphs* or **STG**s – which are a restricted form of Petri nets [Chu87]. This theory has recently been extended to support burst-mode specifications [Chu93].

Another interesting synthesis system was developed by Luciano Lavagno at Berkeley [LKSV91]. This synthesis uses timing analysis to assure that when hazards exist in the circuit, sufficient delays are added to ensure that they are controlled, so that they will not occur in the physical design. Beerel and Ming have also developed analysis and synthesis techniques based on bounded delay methods [BM92].

#### 1.2.2 Architectural Methodologies

Some architectural methodologies are based on design styles which can remove hazards from control logic [Hay81, Hay83, Hol82]. Most of these methods are of restricted applicability, or do not have the performance advantages of the AFSM approach.

Sutherland's micropipeline methodology is the most efficient and successful asynchronous architectural methodology [Sut89]. The micropipeline design style is based on transition logic where the asynchronous rendezvous, or **C-element**, is used to control interaction between hierarchically compositional pipeline stages. There are no direct synthesis tools based on this technique despite the simplicity of the control stages. The most impressive successful application of the micropipelined design style is the asynchronous version of the ARM microprocessor developed by Steve Furber's group at Manchester University called AMULET [FDG+93, Pav94]. The synchronous ARM was the most widely produced RISC processor in the world in the 1980's.

#### 1.2.3 Macro Module Based Design

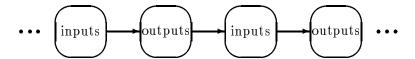

Programming language methods are not targeted for circuit synthesis on the gate and transistor level. Rather, as in programming language compilers, the program instructions are compiled into a set of predefined primitive operations [BS89, vBBK+94, Ebe88, Mar91]. These primitives are a set of asynchronous macro module components such as C-elements, TOGGLEs, MERGE elements, and so forth, that are typically associated with the semantics of the language constructs. The physical design of these macro cells may require an expert asynchronous circuit designer (or one of the AFSM based tools of Section 1.2.1). The area and efficiency of the resultant circuits are very dependent on the primitives chosen. Higher level primitives typically result in larger, slower circuits while lower level primitives normally result in smaller and faster circuits. A significant advantage of this approach over the other two is the relative ease of porting the system to other technologies.

#### 1.3 Silicon Compilation

Software engineers have made remarkable asynchronous circuit synthesis tools using variants of Hoare's CSP programming language for specifications [AG92, Bru91, Bru93a, GA93, Mar91, vBKR+91, vB92b]. These techniques compile down to primitive agents as described in Section 1.2.3, and interesting academic grade implementations have been built [Bru93b, MBL+89]. Brunvand's approach is fully automated, whereas Martin's approach is a directed synthesis system and requires further specification as lower level logic termed production rules. The major drawback of these methods is that the synthesis steps are deemed "correct by construction" so no formal verification is carried out between synthesized implementations and specifications. Deadlock and other properties of a faulty specification may be faithfully implemented, and the source of such errors will be difficult to discover without verification formalisms.

#### 1.4 Formal Methods

Circuit simulation is exponential in time on the input set and device delay variations. Formal proof methods can greatly improve on these results because verification can be carried out hierarchically, values can be abstracted into functions, and regular designs can utilize inductive techniques. The increased complexity of VLSI circuits has produced the demand for logicians to create practical proof systems that can be applied to complex systems.

Several logic systems have been used to verify hardware, including the Boyer-Moore Theorem Prover [Hun86] and higher order logic (HOL) [Sys89, GM93, Gra92,

Mel88, Coh88]. The complex fine-grain logic models have been successful in accurately verifying data path and leaf cells, but are cumbersome for coarser block-level verifications. Hardware designers and engineers usually consider such formal tools of marginal use or even an impediment to the design process because of the time, effort, and theorem proving expertise that is required to utilize such methods.

Success in automating circuit proof systems has been achieved in the asynchronous circuit domain. Ebergen, Udding, and Josephs successfully use trace theory for the formal design and verification of a class of asynchronous circuits that use the delay-insensitive hazard model [Ebe91, Udd84, JU90] (see Section 3.2 for a description of the various hazard models of asynchronous circuits). Dill uses a variant of trace theory to verify circuits using the speed-independent hazard model [Dil89]. His tool was invaluable for the verification of the AFSMs in the Post Office. Process algebras, such as CCS and Circal, have recently been applied to the verification of asynchronous circuits [Bai94, Liu92, MM91, Mol91].

While simulation systems such as VHDL and CSP-based programming languages have been successfully applied to the synthesis of synchronous and asynchronous circuits, automated synthesis has not been achieved with systems capable of formal verification.

#### 1.5 Automated Formal Asynchronous Design

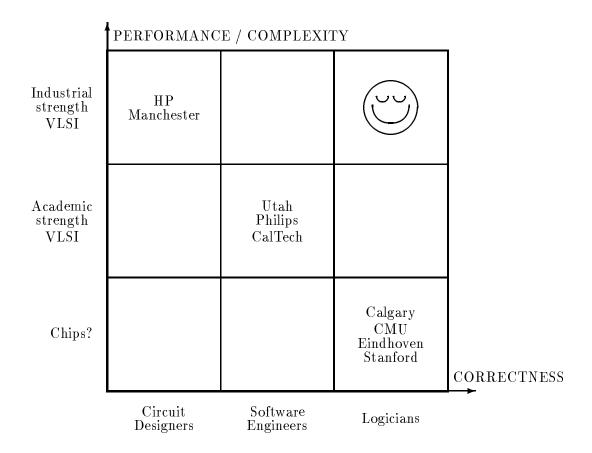

Figure 1.1 partitions the asynchronous design problem space into three columns corresponding to circuit designers, software engineers, and logicians, listing some of the top achievements for each group. The Post Office and the asynchronous ARM

Figure 1.1: Asynchronous Technology Spectrum

at Manchester are engineering feats achieved with almost no tool support by superb circuit designers. On the other end of the scale, mathematical verification has moved from the laboratory into practical use as automated proof systems are being used by engineers for the verification of small circuits and systems. In between is a set of excellent software and systems people who have produced a set of tools capable of automating the arduous task of design synthesis.

The goal of this thesis is to merge the best results from circuit designers, software engineers, and formal mathematicians to work towards a designer's workbench capable of synthesis and automatic verification of asynchronous circuits in such a way that large, complex, parallel ICs can be rapidly prototyped and fabricated.

#### 1.6 The CCS Process Algebra

In the foreword to Milner's book on CCS, C.A.R. Hoare states:

"Concurrency remains one of the major challenges facing Computer Science, both in theory and practice. The wide variation in structure and architecture of concurrent machines is now as great as in the early days of sequential machines . . . Such variation gives rise to confusion and fear of innovation.

Fortunately, progress in theoretical Computer Science brings understanding in place of confusion, and confidence in place of fear. A good theory

reveals the essential unities in computing practice, and also classifies the

important variations. Such a theory was propounded by Robin Milner ten

years ago in his Calculus of Communicating Systems."

Hoare's communicating sequential processes (CSP) and Milner's calculus of communicating systems (CCS) are process algebras, or mathematical systems, that can model and analyze concurrency. This work has applied CCS to the highly concurrent testbed of VLSI circuits, resulting in some practical refinements. CCS is a theoretically satisfactory as well as a practical foundation for the work in this thesis.

CCS relies on the notion of persistent parts, or *agents*, that act independently of each other yet also synchronize. The independence of the actions of agents allows

them to proceed concurrently, and the synchronization of agents occurs with communication. The atomic actions of a system can be represented by a set of symbols called **labels**. These actions can be partitioned into two sets with a "complementation" operation represented by an overbar, extended such that for action  $\alpha$ ,  $\overline{\alpha} = \alpha$ . Assume that  $P, Q, \ldots$  represents processes while  $a, b, \ldots$  (and  $\alpha, \beta, \ldots$ ) represent the actions of a system. The occurrence of an action is represented as

$$P \xrightarrow{a} P' \tag{1.1}$$

meaning that as process P performs the action a it simultaneously evolves into the process P'. These actions are represented as **transition** relations over the processes, and if they are all known the behavior of the system of processes is defined.

Communication is defined as a primitive, atomic interaction between processes. The interaction occurs between a label and its complement. This interaction is further defined as  $handshake\ communication\$ which removes the notion of active (performers or producers) and passive (media or consumers) pairs. If both the label and its complement are offered, the communication can occur; otherwise one of the processes may have to wait. Figure 1.2 shows how processes P and Q can communicate using labels b and c. When a handshake occurs, both P and Q evolve together through an atomic event  $\tau$  into P' and Q'.

Figure 1.2: CCS Communication Interaction

The transitional semantics of such a language is termed a labeled transition system. Since processes are sequential, concurrency arises when independent processes are composed in parallel. When modeling asynchronous systems each component, be it a state machine, register, RAM cell, ALU, or wire, can be modeled as a sequential process that may communicate with other processes. However, most processes can also be decomposed into a smaller set of communicating sequential processes. For example, a certain ALU process could equally be modeled as a parallel set of adder processes. The level of detail of interest will dictate the detail and hierarchy of the description.

#### 1.6.1 Syntax and Semantics of CCS

CCS is a very simple language in both syntax and semantics. The syntax of a CCS process is described by the following BNF description.

The set of actions that an agent can perform is called its **sort**. The special agent Nil can perform no actions, therefore it is the deadlocked or stopped process and its sort is the empty set of actions. CCS is given semantics by induction over the above

structure for agent expressions. The semantics are in terms of the labeled transition system, defined as

$$(S, T, \{ \xrightarrow{\alpha} : \alpha \in T \}) \tag{1.2}$$

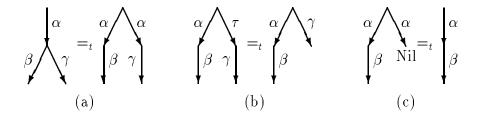

where S is a set of states (or processes), T is a set of transition labels, and the transition relation  $\stackrel{\alpha}{\to} \subseteq S \times S$  for each  $\alpha \in T$ . The transitional semantics are defined by inference from the transition rules of Figure 1.3 where each rule will have zero or more hypotheses and a conclusion.

$$\operatorname{Act} \frac{P \xrightarrow{\alpha} P'}{\alpha . E \xrightarrow{\alpha} E'} \operatorname{Con} \frac{P \xrightarrow{\alpha} P'}{A \xrightarrow{\alpha} P'} (A \xrightarrow{\operatorname{def}} P)$$

$$\operatorname{Sum}_{1} \frac{E \xrightarrow{\alpha} E'}{E + F \xrightarrow{\alpha} E'} \operatorname{Sum}_{2} \frac{F \xrightarrow{\alpha} F'}{E + F \xrightarrow{\alpha} F'}$$

$$\operatorname{Com}_{1} \frac{E \xrightarrow{\alpha} E'}{E \mid F \xrightarrow{\alpha} E' \mid F} \operatorname{Com}_{2} \frac{F \xrightarrow{\alpha} F'}{E \mid F \xrightarrow{\alpha} E \mid F'}$$

$$\operatorname{Com}_{3} \frac{E \xrightarrow{\alpha} E'}{E \mid F \xrightarrow{\pi} E' \mid F'}$$

$$\operatorname{Res} \frac{E \xrightarrow{\alpha} E'}{E \setminus L \xrightarrow{\alpha} E' \setminus L} (\alpha, \overline{\alpha} \notin L) \operatorname{Rel} \frac{E \xrightarrow{\alpha} E'}{E \mid f \xrightarrow{\beta} E' \mid F'}$$

Figure 1.3: CCS Transition Rules

The Act rule, syntactically using the '.' operator called **prefixing**, is the building block for sequential operations. For example, the agent  $\overline{req}.ack$ . Nil can do a  $\overline{req}$  action, followed by an ack action, and nothing more. The constant rule Con defines references to processes, so we can now create recursive, nonterminating agents. For

example, a TOGGLE can now be defined as:

$$TOGGLE \stackrel{\text{def}}{=} a.\overline{b}.a.\overline{c}.TOGGLE \tag{1.3}$$

This definition says that after the first a input the TOGGLE will produce a  $\overline{b}$  output. After the second a transition a  $\overline{c}$  transition is produced. The behavior then repeats.

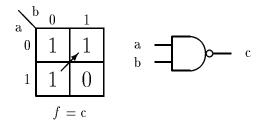

Nondeterministic choice is modeled by the **summation** operator '+' using transitional rules  $Sum_1$  and  $Sum_2$ . A process with summation can behave nondeterministically like any of the summands. The C-element can now be defined by:

C-element

$$\stackrel{\text{def}}{=} a.b.\overline{c}$$

. C-element  $+ b.a.\overline{c}$ . C-element (1.4)

The C-element can behave like either of the two parts; if the a action is taken first, then it evolves into the agent  $b.\overline{c}$ .C-element.

Applying the **relabeling** function f to agent E results in an agent that behaves like E where the labels have been changed according to the function f as expressed by rule Rel. The relabeling function is syntactically expressed as [new/old] where all occurrences of the label old have been replaced by the label new. Relabeling is typically applied to library templates (such as AND gates) where the default labels must be instantiated to the names being used for the specific circuit interconnections.

Concurrent operation is modeled with the **composition** operator '|' using the Com transition rules. Signals can transition independently, expressed by rules Com<sub>1</sub> and Com<sub>2</sub>, and signals with the same label can synchronize in an atomic communication (rule Com<sub>3</sub>). **Restriction**, syntactically represented as a set L, is used

to prevent the restricted agent from actions in the set L, as defined by the side condition to rule Res. This internalizes labels that can communicate in a parallel composition by allowing the internal synchronized action  $\tau$  to proceed uninhibited, and prohibiting the independent actions of the labels from rules  $\mathsf{Com}_1$  and  $\mathsf{Com}_2$ . All communication actions should be restricted in hardware descriptions using CCS.

#### 1.7 Thesis Structure

Chapter 2 uses the fully asynchronous Post Office chip as motivation for higher levels of abstraction and tools supporting asynchronous design and synthesis. The *Mayfly* distributed memory multiprocessor developed at HP is briefly introduced, along with the role of the Post Office in that system. Some advantages and disadvantages of the asynchronous implementation of the Post Office are discussed. Some of the contributions that grew out of this experience of designing an industrial asynchronous chip are included.

Chapter 3 introduces hazards and how they impact asynchronous designs. Asynchronous delay and hazard models are described. The most common combinational and sequential hazards are described with examples, including problems with certain common circuit constructs. Since *no* synthesis system can be hazard free, techniques for hazard removal and controlling unremoved hazards are discussed.

Chapter 4 formalizes burst mode, which I developed in the early stages of the Post Office implementation, in terms of specification and implementation requirements. This permits the automatic verification of terminal burst-mode specifications for the synthesis system presented later in this thesis.

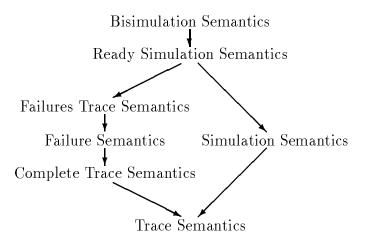

Chapter 5 formalizes the CCS labeled transition system and defines several useful properties including trace equivalence, bisimulation, determinacy, and confluence. The weaknesses in trace semantics are pointed out, motivating the need for stronger bisimulation semantics. A new partial order called **conformance** is introduced. Conformance is aimed at hardware verification and is formally applied to trace and bisimulation semantics formally, and illustrated with several examples.

Chapter 6 introduces Hennessey-Milner process logic and the Modal- $\mu$  calculus. Temporal logics are applied to property testing of asynchronous systems, including a new definition for liveness and deadlock. Other invariant properties that are necessary for complete verification are formalized. A comparison between using process logics and conformance is made for circuit verifications.

Chapter 7 unifies this work in terms of a prototype software tool capable of automatic verification and directed synthesis called **Analyze**. The problems in the CCS notation that prevent CCS from modeling hardware are discussed, including solutions that extend CCS in such a way that retains its advantages of specification clarity. New transitional semantics are presented for these changes. The automated functions of Analyze are discussed. Minimization is an important step of efficient verification, and a new minimization algorithm is presented for branching time bisimulations. Computation interference is then formalized. The steps necessary to formally verify a valid burst-mode specification are shown. The high level top-down synthesis process is then described, including the support supplied by Analyze.

Chapter 8 contains hindsights gained from the development and limited application of the Analyze tool, and areas of further research are discussed.

### 1.8 Contributions

The major contributions of this dissertation include the following:

- 1. A software prototype CAD tool called *Analyze* was developed and described in this dissertation. It is the first tool to utilize multiple equivalences appropriate for hardware. It also includes all of the common hazard models of asynchronous circuit analysis and verification. The tool is designed using compositional methods and is one or more orders of magnitude faster than the Concurrency Workbench for comparable problems.

- 2. A new theory for loose specifications based on partial orders is developed. Partial orders sufficient for verification of asynchronous hardware systems are formalized using both trace and bisimulation semantics. Formal verification uses these partial orders as the foundation of conformance between a specification and its refinement (possibly as an implementation).

- 3. Weaknesses in the CCS labeled transition system have been formally fixed with new transition rules and a meta evaluation rule based on computation interference principles which allows direct representation and analysis of asynchronous hardware modules as CCS processes. Analyze implements these changes in a mixed-mode fashion, allowing standard CCS transition rules as well as the new conjunctive parallel composition operator.

- 4. The burst-mode model remains an important foundation of this work even though its invention preceded the work in this thesis. The specification and

implementation requirements are formalized and the requirements for the verification of terminal specifications is laid out. Completely automating the validation of a burst-mode specification is not always possible because of the constraints on the environment.

- 5. A high level synthesis procedure, supported by the Analyze tool, is developed.

These steps can be used to test different approaches and can, with supporting module layout and place and route software, rapidly produce verified industrial strength low latency asynchronous systems.

- 6. New definitions for liveness and deadlock for parallel processes is formalized.

Other logic macros are defined that simplify the process of total verification.

These logics can be applied to a previously available tool called the Concurrency Workbench.

# Chapter 2

# Motivation for Analyze

In the late 1970s and early 1980s asynchronous circuits and systems, such as the DDM machines [Dav77], were built out of small scale integrated components on wire wrap boards. State machines were built using gates, EPROMs, muxes, and other devices where the handshake signals were all accessible. Switch and light panels that could intercept handshake signals and logic probes usually sufficed as test jigs. The added complexity and inaccessibility of signals in integrated LSI circuits ([Ste84, Hay83]) increased the difficulty of testing and designing asynchronous systems, but their low level of integration coupled with the modularity of asynchronous protocols made implementations feasible. Even so, the primary goal of all these circuits was to demonstrate operational feasibility and supply academic proofs of concept; circuit performance was not an issue.

However, performance was critical to the success of the full-custom CMOS VLSI Post Office chip begun in 1987 [SRD86, CDS93b]. The complete chip is the largest and most complex fully asynchronous integrated circuit in published work. It consists of approximately 300,000 transistors and over 95 different finite state machine controllers with an external bandwidth of 300 megabytes per second.

I was responsible for the architectural design and implementation of this chip. The sheer level of integration available coupled with performance requirements created problems which could not be hidden by the modularity of asynchronous interfaces. Many lessons were learned as design techniques were rationalized, mechanized,

and formalized. Hindsight proved to be a valuable tutor in many areas, leading to the more advanced and integrated tool Analyze developed herein.

This chapter uses experiences from the design of the Post Office, including small design vignettes, to demonstrate the need for the improved methodologies and tools presented in this thesis.

# 2.1 Overview of Mayfly and the Post Office

The Mayfly architecture is a general purpose parallel processor, often called a distributed ensemble architecture [DCH+89, Dav92]. Multiple processing elements (or PEs) cooperate to solve single complex problems which have been broken into smaller parallel computations. There is no globally shared memory. Task spawning and communication between processes on different PEs are carried out via message passing. The Post Office chip is the communication coprocessor which supports this internode message passing.

| Al Davis         | General architecture, processor board, & context cache |

|------------------|--------------------------------------------------------|

| Bill Coates      | I-Cache, Post Office interface board, & PO RAM cells   |

| Robin Hodgson    | Runtime software & debugging                           |

| Richard Schediwy | Data cache                                             |

| Ken Stevens      | Post Office design & implementation                    |

Table 2.1: Mayfly Design Responsibilities

The Mayfly team consisted of five people with responsibilities as shown in Table 2.1. The top level architecture and programming principles were developed by Al Davis at Fairchild/Schlumberger and Hewlett-Packard in the mid to late 1980s. The

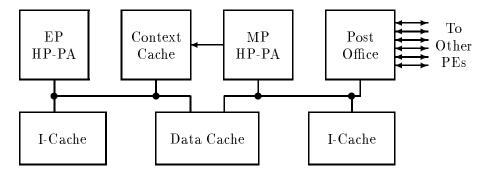

programming language and compiler is a parallel variant Scheme (a Lisp language) developed at the University of Utah under the direction of Bob Kessler. The Mayfly hardware was built at Hewlett-Packard. Figure 2.1 shows the major components of a single Mayfly PE. A Mayfly PE consists of two Hewlett-Packard Precision Architecture (or HP-PA) RISC processors. One processor is responsible for executing user code (the EP or evaluation processor), while the other processor is responsible for all system overhead (the MP or maintenance processor). MP tasks include setting up the run list and packetizing messages for delivery. These two processors execute in parallel.

Figure 2.1: Mayfly Processing Element Block Diagram.

The circuits used in the Mayfly design consisted of custom HP-PA processor chips, programmable logic devices, glue logic, memory components, and the full custom Post Office chip. Al Davis designed and built the processor motherboard and novel context cache. Parallel data structure access is facilitated by a 4-page dual ported data cache, built by Richard Schediwy. Bill Coates designed and built the instruction cache and Post Office interface board.

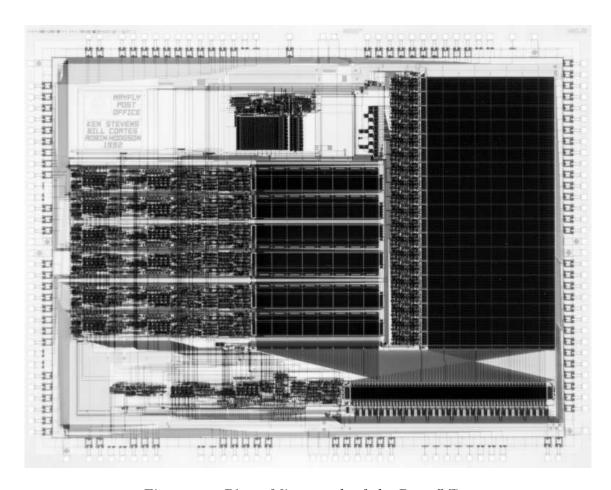

The Post Office architecture and communication topology were designed by myself [Ste86]. The design was taken from concept to a complete VLSI implementation

between 1985 and 1991. The Post Office handles all physical communication aspects of message passing in the Mayfly processor. It includes subsystems for handling adaptive routing, buffering, transmissions and retransmission, congestion and deadlock avoidance. First silicon was complete in February 1991. The final version was completed at the University of Calgary and fabricated in November 1992.

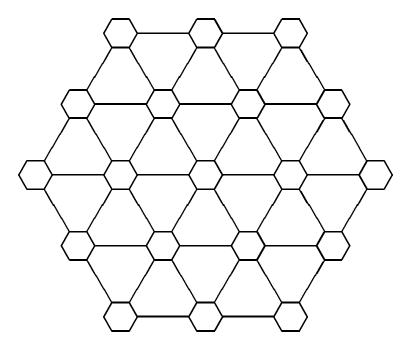

The topology (shown in Figure 2.2) and architectural design were created during 1985 and 1986. Helios [Kra85], a distributed simulation tool which ran on networked Symbolics Lisp machines, was used for register transfer level simulations. The Post Office was implemented as a single VLSI integrated circuit, and was laid out entirely by hand using the Electric system [Rub87]. I designed and implemented the entire chip, including the pads, with the exception of the RAM cells and driver circuitry which were laid out by Bill Coates. Simulations of the layout used COSMOS [Car], a switch-level simulator. I tested all the fabricated chip fragments on an IMS tester. The complete chip was tested in a single Mayfly node. Robin Hodgson wrote device drivers and runtime system software. He tested the Mayfly and first and final silicon of the Post Office extensively, although I did much of the initial testing of the first silicon.

The Mayfly interconnection network is a hexagonal mesh wrapped as a twisted torus resulting in the provably minimal diameter [Ste86]. This creates what is known as a processing *surface*. Surfaces have hexagonal boundaries themselves and can be interconnected by abutment in a hexagonal mesh to form a two-level "recursive" topology. The Post Office is therefore a seven ported device. It physically connects to six other adjacent processing nodes in the surface via six 8-bit bidirectional external ports. There is also an internal 32-bit word-wide PE port through which the Post

Figure 2.2: Mayfly Interconnection Topology

Office can access the processor cache and local memories for message retrieval and delivery. The Post Office design permits simultaneous transmission on all seven ports. Measured performance in a seven node Mayfly prototype indicates that all six external ports can sustain transfers at an average rate of 50 megahertz, for an aggregate network delivery bandwidth of 300 megabytes per second.

Performance is critical to the Post Office since communication latency is key to the distributed memory Mayfly system. Bandwidth utilization of the links between the Post Office chips must be optimized to achieve a performance that scales with the architecture. Hence a packet switched system was chosen. Virtual cut-through [KK79] was employed because it allows packets to be forwarded to the next destination as soon as the header is received, resulting in a "pipelined" delivery across many chips. Packets which cannot be forwarded immediately are buffered centrally in the

Post Office chip in order to free the external link for other packet traffic. When the destination ports are free, the packet will be forwarded through one of those links. Cut-through is not used in the source and destination Post Office chips; the packets are placed directly into the buffer pool. Although this increases message latency, it insulates packets from any delays that may be encountered in the software protocols that load and unload packets from the Post Office and the Mayfly PE. This results in better utilization on the communication links, and permits the implementation of the external ports to use the smaller dynamic logic (as opposed to the static logic required for the PE interface and the central buffer pool and logic).

The Post Office effort was challenging for several reasons:

- It was a pioneering coprocessor for distributed ensemble routing architectures.

Its design preceded CalTech's wormhole routing [DS87] and multi-queue architectures [TF92].

- 2. The design is massively parallel, with a complex control structure.

- 3. The Post Office is an asynchronous chip placed into a synchronous environment.

- 4. It is the most complex fully asynchronous single integrated circuit in published work.

- 5. It was built in a commercial environment where performance was an important aspect.

## 2.2 Asynchrony in Mayfly

#### 2.2.1 Features

The Post Office is an island of asynchrony in an otherwise fully synchronous architecture. The processors in the Mayfly are synchronous HP-PA machines using synchronous bus protocols. The decision to design the Post Office as a fully asynchronous part was based on a number of factors, including the robustness of asynchronous interfaces, scalability, and the desire to build a practical, complex device which is superior to synchronous techniques. The scalability of the Mayfly architecture is probably the single most important argument in favor of an asynchronous Post Office design. The physical extent of the Mayfly architecture is formally unbounded, and the size of an implementation is only limited by the size of the address word. The current Post Office chip supports instantiations of up to 519,841 PEs. The ability to arbitrarily scale the architecture poses serious technical problems if a global clock is necessary to synchronize operations. Clock skew can be a problem in itself for synchronous design as technology progresses [Bak90]. For extensible systems such as the Mayfly where the PE count is unbounded, synchronizing all of the nodes with a single clock becomes intractable.

The robustness of functional, asynchronous interfaces removes the problems of clock skew and simplifies link arbitration and transfer synchronization. Mayfly processors are composed by simply plugging the Post Office links together (subject to topological constraints). Each PE in the multiprocessor contains a local crystal and a clock generator that runs at its own clock speed. Processor speeds for communication between PEs are irrelevant due to the asynchronous interface. One PE in the

HP prototype running at an internal clock speed of 16 MHz communicates perfectly well with another running at 64 MHz via the Post Office chips.

Additionally, the arrival times of packets from the external ports and the PE can be completely random. In a synchronous system, these arrivals would have to be normalized to the system clock, resulting in slower delivery. Receptive asynchronous systems begin processing packets as soon as data arrives [NDDH93]. This robustness of interfaces is also being investigated for commercial applications in noisy environments [MCS94].

The low power nature of asynchronous architectures was one further advantage demonstrated in the Post Office. Asynchronous circuits contain fine grain, dynamic power management due to the handshake protocols. Each idle Mayfly PE requires 30 amperes of current at 5 volts. By way of contrast, the Post Office, which is the only asynchronous part in the system, uses only 2 milliamps when idle.

## 2.2.2 Problems

In a clocked system, care must be taken to assure that the clock signal has a short rise and fall time, that noise is minimized (ringing, overshoot and undershoot, etc.), and that the clock is driven to the power and ground rails. The same restrictions exist on the handshake signals in asynchronous systems. Although there are many more handshake signals than clocks, handshakes are generally localized between pairs of controllers, on the same integrated circuit, with low capacitive loading. For example, the clock and drivers inside the synchronous alpha chip are global and highly loaded taking up 30% of the chip area and nearly 60% of the power, resulting in considerable technical problems [Com92]. When asynchronous handshake signals are not local,

such as between processing elements in the Mayfly, care must be taken to assure that failures do not occur due to violations of the assumption that signals are "digital".

In the Mayfly prototype, each processor had a separate clock generator and power supply. Mayfly PEs are easily composable through the Post Office because the functional interface scales well and is not subject to failures due to synchronization, arbitration, or device speed or clock speed variations. However, communication was susceptible to failures when (i) voltages varied significantly between nodes, (ii) when crosstalk was a significant problem, (iii) when the impedance of the drivers and receivers were not matched such that ringing occurred, and (iv) due to current variations that cause power supply noise. These faults are all due to physical properties that violate the digital assumption, and they can be cumulative. As an example, the request handshake signal, driven from the power supply of one Post Office PE, may be received by another Post Office chip with a different power supply. If there is a significant difference in voltages, switching thresholds may not be reached, and very small amounts of noise on the line could cause the receiver to perceive unintended changes in the binary value on the line.

Noise perceived as a switch in logic levels on handshake signals in asynchronous systems and in clocked systems can both result in failures, but they may be more severe in asynchronous machines. Illegal voltage changes to a state machine can result in the circuit deadlocking or switching to an improper state. This generally will result in illegal outputs which can ripple the effect if the outputs are also control lines. Noise can result in similar effects in the controllers of a synchronous system.