## Fundamentals of Digital System Design

ECE/CS 3700

Spring 2018, Homework # 1 Due Date: Monday, Jan 29, 2018 Please deposit the HW in the ECE/CS 3700 HW locker # 26 in MEB 2<sup>nd</sup>-floor. HW lockers are located near MEB 2325.

**Note:** The following set of questions correspond to chapter 2 in the textbook. I would advice you to go through chapter 2 (omit the Verilog related section 2.10 and the K-map related sections 2.11 onwards), and Sec B.3 in Appendix B (CMOS gates), before solving these problems. The homework is due by Jan 29. Show all your work. Should you have difficulty in understanding any of the questions, feel free to ask the TAs or the instructor. Good luck!

- 1) (Simplification using Boolean Algebra 10 points) Using the laws of Boolean algebra, and not by using truth tables, prove (or disprove) the following:

- a)  $(X+Y) \cdot (X+\overline{Y}) = X$

- b)  $(X) \cdot (X + Y) = X$

- c)  $(X) \cdot (X + \overline{Y}) = X$

- d)  $(X+Y) \cdot (\overline{X}+Z) = XZ + \overline{X}Y$ . By the way, we have studied this function in class. What is it?

- e)  $X \cdot Y \cdot Z + X \cdot \overline{Y} = X \cdot \overline{Y} + X \cdot Z$

- 2) (10 points) Simplify the following expressions as much as possible:

- a)  $(x+y)(\overline{x}+y)(x+\overline{y})(\overline{x}+\overline{y})$

- b)  $\overline{x}(\overline{y} + \overline{z})(x + y + \overline{z})$

- c)  $\overline{A} \cdot B \cdot (\overline{D} + \overline{C}D) + B(A + \overline{A}CD)$

- d)  $x \cdot y + y \cdot z + \overline{x} \cdot z$ .

- 3) (3-var XOR/XNOR 15 points) In class, we have analyzed the Exclusive-OR (XOR) function of two variables: f(a, b), which is represented as f = a ⊕ b = ab' + a'b. Similarly, the XNOR function of two variables, g(a, b) = a ⊕ b = a⊕ b = a'b' + ab. You will now analyze the 3-variable XOR/XNOR functions:

- Take the 3-variable function f(a, b, c) = a ⊕ b ⊕ c. This function is really the XOR(a, b, c). Write down the truth-table, the ON-set minterms and obtain a simplified sum-of-product (SOP) form expression for the function. [Does there exist any simplification of this SOP form?]

- Now consider the 3-variable function  $f(a, b, c) = \overline{a \oplus b \oplus c}$ . Think about it as a NOT of XOR(a, b, c). Obtain its minimized SOP form. [Again, does there exist any SOP form simplification?]

- Now consider the function  $f(a, b, c) = a \overline{\oplus} b \overline{\oplus} c$ , which is *curiously* called the 3-variable XNOR function.

Think of f as  $f = a \overline{\oplus} b \overline{\oplus} c = (a \overline{\oplus} b) \overline{\oplus} c = a \overline{\oplus} (b \overline{\oplus} c)$ . Construct the truth-table for this function, and derive the minimal SOP form for the function. Do you notice how  $f = a \overline{\oplus} b \overline{\oplus} c = a \oplus b \oplus c$ ?

- By the way, XOR/XNOR functions have many interesting properties; one of which you are asked to prove (or disprove): f(a, b) = a ⊕ b = a ⊕ b = a ⊕ b.

- 4) (A Digital Design Example 15 points) You are asked to design the following warning circuit for your car. The warning signal W should be set to high voltage (logical 1) if: (i) the engine is running and the door is open; OR (ii) with the engine running, and somebody sitting in the driver's seat, and the belt is not fastened. Otherwise the output of the circuit is 0. The circuit should rely on the following sensors:

- Sensor from the engine (C=1 if engine is running, otherwise it is 0);

- Seat sensor (S=1 if somebody is sitting on the seat, otherwise 0);

- Door sensor (D=1 if the door is closed, otherwise 0);

- Belt sensor (B=1 if it the belt is fastened, otherwise 0).

Derive the truth table corresponding to the above specifications. Subsequently, derive a simplified Boolean expression and draw the logic circuit using AND, OR and NOT gates.

5) (Minterms and Maxterms - 20 points) Consider the Boolean function f(x, y, z) represented by the truth table shown in Table I.

| _ |   |   |   |   |

|---|---|---|---|---|

|   | x | y | z | f |

| ſ | 0 | 0 | 0 | 1 |

|   | 0 | 0 | 1 | 0 |

|   | 0 | 1 | 0 | 1 |

|   | 0 | 1 | 1 | 1 |

|   | 1 | 0 | 0 | 0 |

|   | 1 | 0 | 1 | 0 |

|   | 1 | 1 | 0 | 1 |

|   | 1 | 1 | 1 | 1 |

TABLE I Truth Table

- a) Derive the Minterm Canonical form (Sum of Minterms) expression of the Boolean function from the truth table.

- b) Simplify the derived minterm canonical form as much as possible.

- c) Derive the Maxterm Canonical form (also called the Canonical Product-of-Sum form) expression of the Boolean function from the truth table.

- d) Is the minterm canonical form of the function logically equivalent to its maxterm canonical form? If yes, prove the equivalence of the expressions. If not, prove otherwise.

- 6) (CMOS Logic Gate Design 10 points) Recall that CMOS logic gates consist of a pull-down and a pullup network comprising of NMOS and PMOS transistors, respectively. Moreover, CMOS gates implement

*inverting* logic. Keeping this in mind, design a CMOS gate that implements the following Boolean expressions. Note that you are asked to design just one logic gate implementing the entire Boolean function. Use as few transistors as possible. Make sure to label the input (gate of each transistor) variables accordingly. Furthermore, don't forget to show where the output of the logic gate is.

- a)  $\overline{A} + \overline{B} + \overline{C}$

- b)  $(\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D})$

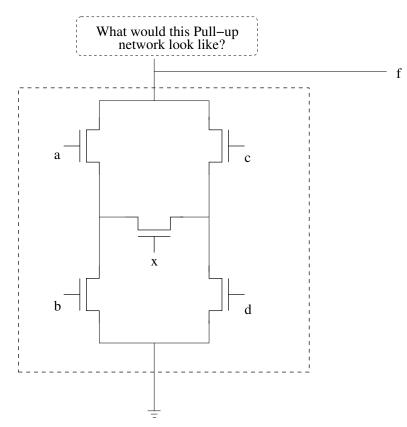

- 7) (Pull-Up/Pull-Down Network in CMOS gates 20 points) Consider the pull-down network (consisting of NMOS transistors) of a CMOS gate as shown in Fig. 1. Construct the corresponding pull-up network consisting of PMOS transistors. Recall, the pull-up and pull-down networks are *duals* of each other. Also, derive the logic function implemented by the gate. Briefly state the reasoning behind your design.

Fig. 1. Pull-down network of the gate is shown. Draw its corresponding pull-up network.

In addition to the above questions, I'm giving you a list of some exercise problems from the book that you can try to solve to gain some more practise with Logic Design and Simplification. These are not part of the HW, and they will not be graded. This is just a suggested exercise for you: Problems: 2.7, 2.12, 2.35.